Synopsis

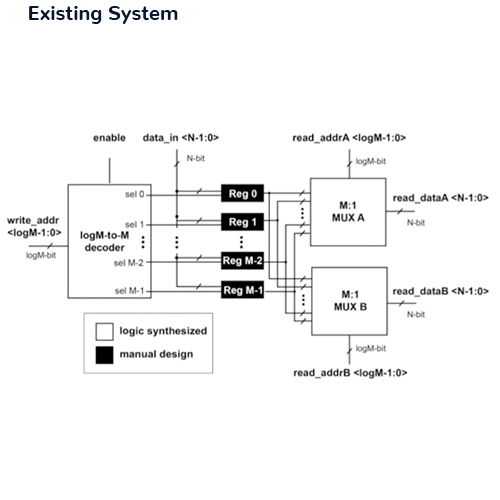

Electricity usage in global data centers is estimated 200 terawatts hour (TWh) each year, or about 1% of the total electricity consumed. This significant amount of energy consumption has become a critical problem in modern society, and gives importance for the urgent requirement for energy-efficient computing technologies. In the existing system, the design of M-word×Nbit register files by adopting a top-down design flow with the established synthesis framework. Although the autosynthesis methodology resulted in increasing chip resource utilization, the design efficiency is significantly enhanced.

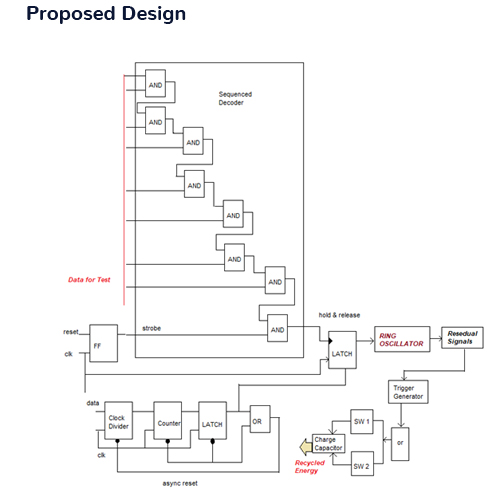

Since the scale of AQFP chips will be extended towards tens of thousands of Josephson junctions, an automatic design flow using electronic design automation (EDA) tools is of critical importance for circuit design. In the proposed system, the benefit of adiabatic system is further improved by implementing the AQFP based sequential circuits design. further extension of the current design flow to support sequential logic synthesis is highly desirable; meanwhile, further optimization of the inserted buffers and splitters will be our next research focus.

Proposed system

In the proposed system, the benefit of adiabatic system is further improved by implementing the AQFP based sequential circuits design. further extension of the current design flow to support sequential logic synthesis is highly desirable; meanwhile, further optimization of the inserted buffers and splitters will be our next research focus.

Solution Statement

- Complex circuitry is implemented to verify the power recycling principle

Reviews

There are no reviews yet.