Objective

To design an effective low power pipelined architecture for neural sorting algorithm

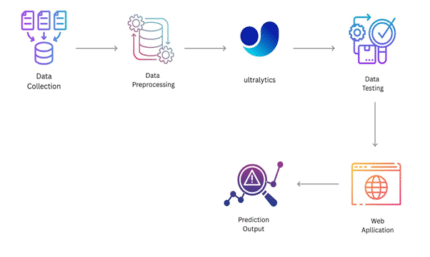

This project presents the design and implementation of a Neural Sorting Algorithm (NSA) using a pipelined architecture with configurable sorting controls, aimed at enhancing the efficiency and adaptability of sorting operations in real-time applications. Traditional sorting algorithms, such as QuickSort and MergeSort, are often inefficient in handling large or dynamically changing datasets. The proposed neural sorting algorithm leverages artificial neural networks (ANNs) to learn and predict the optimal order of data, providing a more flexible solution that adapts to specific sorting tasks. To optimize the performance of this algorithm, a pipelined architecture is employed, enabling parallel processing of multiple data elements at each stage, reducing the overall sorting time and improving throughput. The architecture features configurable sorting controls, which allow users to fine-tune parameters such as the number of pipeline stages, data partitioning, and neural network configuration, based on the size and nature of the input data. This flexibility ensures that the system can be adapted to a wide range of applications, from embedded systems with limited resources to large-scale data centres. The proposed design also focuses on resource efficiency, minimizing power consumption and gate count while maximizing sorting throughput.

Through simulations and performance evaluation, the project demonstrates that the neural sorting algorithm implemented in the pipelined architecture offers significant improvements in sorting speed, scalability, and energy efficiency compared to traditional sorting approaches, making it an ideal solution for modern computational environments that require high-performance, adaptable, and resource-efficient sorting capabilities.

Existing system

In the existing system, sorting cycles are significantly reduced by enhancing the parallelism of the architecture, which leads to improved performance and efficiency. The configuration involves sorting 2048 32-bit data elements, with 16 data elements processed simultaneously in each cycle. By leveraging this parallelism, the proposed architecture can outperform existing sorting designs in key performance metrics. Specifically, it achieves a 16% improvement in the throughput-to-gate-count ratio, meaning it delivers higher sorting throughput without a proportional increase in the number of logic gates required. This reduction in gate count helps optimize resource utilization, making the design more compact and cost-effective. Additionally, the throughput-to-power-consumption ratio improves by 25%, highlighting the energy efficiency of the architecture. The design achieves this efficiency by processing multiple data elements in parallel, which reduces the overall number of cycles required to complete sorting tasks and consequently lowers power consumption. Ultimately, the provided architecture maximizes the use of hardware resources by ensuring that both throughput and power consumption are optimized, providing a highly efficient sorting solution that is well-suited for resource-constrained environments.

Problem statement

- The major drawback includes, sorting is not effective for all values

- The processing latency is more in existing hybrid sorting process

Proposed system

The proposed neural sorting algorithm leverages artificial neural networks (ANNs) to learn and predict the optimal order of data, providing a more flexible solution that adapts to specific sorting tasks. To optimize the performance of this algorithm, a pipelined architecture is employed, enabling parallel processing of multiple data elements at each stage, reducing the overall sorting time and improving throughput. The architecture features configurable sorting controls, which allow users to fine-tune parameters such as the number of pipeline stages, data partitioning, and neural network configuration, based on the size and nature of the input data.

Reviews

There are no reviews yet.